ARM’s Digital Signal Controllers, Cortex-M4 and Cortex-M7, address the need for high-performance generic code processing as well as digital signal processing applications. The …

M4 M7 COMPARISION - Architectures and Processors forum

2015年8月10日 · First of all: Most of the differences between the Cortex-M4 and Cortex-M7 bring only improvements. I say most, because the Cortex-M7 cost a little more. The short answer is …

Cutting Through the Confusion with Arm Cortex-M Interrupt …

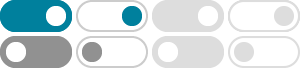

2014年2月28日 · The number of priority levels in the Arm Cortex-M core is configurable, meaning that various silicon vendors can implement different number of priority bits in their chips. …

Cortex-M4: guaranteed wakeup from WFI? - Arm Community

2013年8月8日 · The ATmega* processors have a very simple solution to this problem: enabling interrupts is always delayed by one clock cycle such that the processor can safely enter sleep …

Building Safe and Secure Software with Rust on Arm - Arm …

2024年11月11日 · This popular microcontroller features an Arm Cortex-M4 processor, along with 256 KiB of SRAM and 1 MiB of Flash. Bare-metal Rust firmware for Arm Cortex-M can rely on …

on the market with multiple processors. For example, the NXP LPC4300 contains an ARM Cortex-M4 and a Cortex-M0 processor, and the Freescale Vybrid contains a Cortex-M4 and a Cortex …

Arm Cortex-M resources - all in one place

2017年2月20日 · The DSP capabilities of Arm Cortex-M4 and Cortex-M7 Processors: Cortex-M4 and Cortex-M7 in DSP applications: link: How to use the Python wrapper for CMSIS-DSP with …

Cortex M4 exception return sequence - Arm Community

2014年12月14日 · So there's no real difference in writing an interrupt-routine and a normal subroutine for a Cortex-M based microcontroller. I remember in the 80's (speaking about the …

Cortex M4 - Keil forum - Support forums - Arm Community

I have installed MDK ARMv4.12 and trying to test whether Cortex M4 works correctly. 1. Created a new project and added Cortex M4 as device under 'ARM' (No start

Interruptible Instructions on Cortex-M4 - Arm Community

The ARM Cortex-M4 Processor Technical Reference Manual states: To minimize interrupt latency, the processor abandons any divide instruction to take any pending interrupt. On return …